# New Design Method of Uniform and Nonuniform Distributed Power Amplifiers

Cedric Duperrier, Michel Campovecchio, Laurent Roussel, Monique Lajugie, and Raymond Quéré, *Senior Member, IEEE*

**Abstract**—A new design methodology of uniform and nonuniform distributed power amplifiers is reported in this paper. This method is based on analytical expressions of the optimum input and output artificial lines making up the uniform and nonuniform distributed architectures. These relationships are derived from the load-line requirement of each transistor size for optimum power operation. Furthermore, specific design criteria are presented to enable an efficient choice between uniform and nonuniform distributed architectures. To validate this new design methodology, a nonuniform distributed power amplifier has been manufactured at the TriQuint Semiconductor Foundry, Richardson, TX, using a  $0.25\text{-}\mu\text{m}$  power pseudomorphic high electron-mobility process. This single-stage monolithic-microwave integrated-circuit amplifier is made of six nonuniform cells and demonstrates 1-W output power with 7-dB associated gain and 20% power-added efficiency over a multi octave bandwidth.

**Index Terms**—Distributed amplifiers, design methodology, impedance matching, MMIC power amplifiers.

## I. INTRODUCTION

MONOLITHIC-microwave integrated-circuit (MMIC) power amplifiers are highly necessary for broad-band microwave communication systems and radars. Criteria such as maximum power and maximum efficiency, but also high reliability and high integration, are the most important issues.

The basic principle of distributed amplification overcomes the limitations related to finite gain-bandwidth product by paralleling devices so that their gate and drain capacitances are absorbed into artificial transmission lines. Unfortunately, several power-limiting mechanisms can be identified within distributed amplifiers [1], [2]. Indeed, each transistor demonstrates a strongly frequency-dependent power behavior so that the overall output power is only a small fraction of the combined power capabilities of all active devices [3], [4]. Distributed amplification has already demonstrated high performances for small-signal broad-band operation, but its power behavior must be carefully optimized using suited design methodologies.

A new design methodology based on nonuniform distributed power amplifiers is reported in Section III as a generalization of our previous work on uniform distributed power architec-

Manuscript received March 30, 2001; revised August 1, 2001. This work was supported by the French Direction Générale de l'Armement.

C. Duperrier and M. Campovecchio are with the Institut de Recherche en Communications Optiques et Microondes Laboratory, University of Limoges, 87060 Limoges, France (e-mail: cedric@ircm.unilim.fr).

L. Roussel and M. Lajugie are with the Thales Microwave Laboratory, 91349 Massy, France.

R. Quéré is with the Technology Institute of Electrical Engineering, 19100 Brive, France.

Publisher Item Identifier S 0018-9480(01)10437-0.

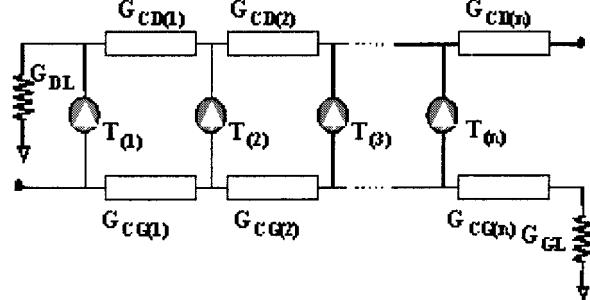

Fig. 1. Distributed power amplifier ( $n$  cells).

tures [5]. The design parameters of artificial gate and drain lines are expressed as a function of the optimum power load of each FET size providing both the initial values and right directions in which the optimum tradeoff can be reached between wide-band and high-power operation.

Furthermore, Section III presents specific design criteria that enable to efficiently choose between uniform and nonuniform distributed architectures. Those design criteria are illustrated by the particular case of the MMIC nonuniform amplifier reported in Section IV.

## II. DESIGN METHODOLOGY OF UNIFORM DISTRIBUTED POWER AMPLIFIERS

A distributed amplifier is called uniform if all transistors are identical. The design methodology of uniform power distributed amplifiers [5] is derived from the power matching conditions of each transistor and the equalization of their control voltages over the entire frequency band. It enables the analytical determination of artificial gate and drain-line characteristics as a function of the optimum power load required by each transistor.

Fig. 1 shows the general architecture of a distributed amplifier where the  $i$ th transistor is called  $T_{(i)}$  ( $i = 1$  to  $n$ ). The optimum characteristic conductances of gate and drain-line sections are, respectively, called  $G_{CG(i)}$  and  $G_{CD(i)}$ , while the gate and drain dumping loads are, respectively, called  $G_{GL}$  and  $G_{DL}$ . It should be noted that the optimum input and output capacitances ( $C_{IN(i)}$ ,  $C_{OPT(i)}$ ) of each device are, respectively, absorbed into the artificial gate and drain lines to synthesize the optimum characteristic conductances  $G_{CG(i)}$  and  $G_{CD(i)}$ .

### A. Optimum Power Load

For power-amplifier design, one of the key points is the determination of the optimum input/output power loads that maximize the device output power  $P_{max}$  at 1-dB compression. The

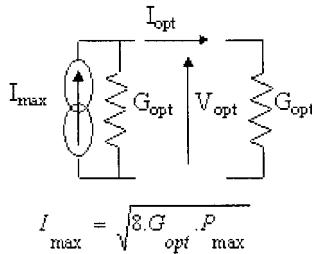

Fig. 2. Optimum power state of the device loaded by  $G_{\text{opt}}$ .

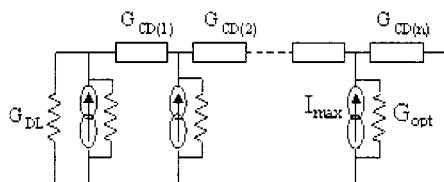

Fig. 3. Equivalent drain line for optimum design.

optimum power loads can either be determined by nonlinear simulations or by load-pull measurement [6]. As generally confirmed by experimental results on FETs, the conjugate of the optimum output power load is almost equivalent to a constant conductance  $G_{\text{OPT}}$  in parallel with a constant capacitance  $C_{\text{OPT}}$  over very wide bandwidths

$$Y_{\text{opt}}(\omega) = G_{\text{opt}} - j \cdot C_{\text{opt}} \cdot \omega \quad \forall \omega \in [\omega_{\min}, \omega_{\max}]. \quad (1)$$

We have already demonstrated that the same conclusion on constant ( $G_{\text{opt}}$ ,  $C_{\text{opt}}$ ) is true for optimized cascode devices [7] so that the design methodology reported in this paper can be directly applied to cascode distributed amplifiers.

Therefore, the optimum power state of each transistor within a distributed amplifier requires equal control voltages and optimum power loads seen by each active device over the entire frequency band.

### B. Drain-Line Design

In the particular case of uniform distributed amplifiers, the drain-line profile has to be synthesized for loading all devices with the same optimum output admittance  $Y_{\text{opt}}$ .

Since the optimum output capacitance  $C_{\text{opt}}$  of each transistor is absorbed into the artificial drain line, the power optimization consists of loading the equivalent output generator of the transistor with the optimum power load  $G_{\text{opt}}$  (see Fig. 2). When transistors are replaced by their equivalent generator, the resulting drain line is shown in Fig. 3, where each drain section  $G_{\text{CD}(i)}$  must be synthesized to load each device generator ( $I_{\max}$ ,  $G_{\text{opt}}$ ) by its optimum conductance  $G_{\text{opt}}$ .

In the uniform case, assuming an identical gate voltage amplitude on each transistor (see Section II-C), the characteristic conductances  $G_{\text{CD}(i)}$  of the drain-line sections are given by

$$G_{\text{CD}(1)} = G_{\text{opt}} \quad (2)$$

$$G_{\text{CD}(i)} = G_{\text{opt}} \left( \frac{G_{\text{opt}}}{G_{\text{opt}} + G_{\text{DL}}} + (i - 1) \right), \quad 2 \leq i \leq n. \quad (3)$$

The resulting optimum output power  $P_{\text{out}}$  of the uniform distributed amplifier is

$$P_{\text{out}} = \left( \frac{G_{\text{opt}}}{G_{\text{opt}} + G_{\text{DL}}} + (n - 1) \right) \cdot P_{\max} \quad (4)$$

where  $n$  is the total number of transistors within the amplifier.

Indeed, for moderate bandwidth applications ( $f_{\max}/f_{\min} < 3$ ), the amplifier output matching is not so critical, and we have already demonstrated that the dumping drain load  $G_{\text{DL}}$  may be suppressed [7]. Nevertheless, in order to consider the most general case of very large bandwidths, all equations take  $G_{\text{DL}} \neq 0$  since setting  $G_{\text{DL}} = 0$  in (3) and (4) enable to derive the optimum case for moderate bandwidths.

### C. Gate-Line Design

In the same manner as in the drain-line case, the optimum characteristic conductances  $G_{\text{CG}(i)}$  of the gate line can be determined to match the equivalent input conductances  $G_{\text{IN}(i)}$  of transistors  $T_{(i)}$  so that equal gate voltage amplitudes can be obtained over the frequency band. The equivalent input capacitances  $C_{\text{IN}(i)}$  are absorbed into gate-line sections to synthesize the optimum characteristic conductances  $G_{\text{CG}(i)}$  (see Fig. 1).

To achieve the equal gate voltage condition, the characteristic conductances  $G_{\text{CG}(i)}$  and the gate dumping load  $G_{\text{GL}}$  of uniform distributed amplifiers are given by

$$G_{\text{CG}(i)} = \sum_{k=i}^n G_{\text{IN}}(f_{\max}) \quad \text{and} \quad G_{\text{GL}} = G_{\text{IN}}(f_{\max}). \quad (5)$$

It should be noted that the equivalent input conductances  $G_{\text{IN}(i)}$  are frequency dependent, which makes the gate matching accurate at a single frequency. However, when the characteristic conductances  $G_{\text{CG}(i)}$  are determined at the maximum operating frequency  $f_{\max}$  (5), an almost constant gate voltage amplitude can be reached over wide frequency bands.

Moreover, in order to meet the condition of equal phase velocities on the gate and drain lines, the electrical lengths  $\theta_{\text{CG}(i)}$  and  $\theta_{\text{CD}(i)}$  of the corresponding artificial gate- and drain-line sections must verify

$$\theta_{\text{CG}(i)} = \theta_{\text{CD}(i)} \quad \forall i = 1, \dots, n. \quad (6)$$

### D. New Design Criterion—Choice of Uniform and Nonuniform Distributed Power Amplifiers

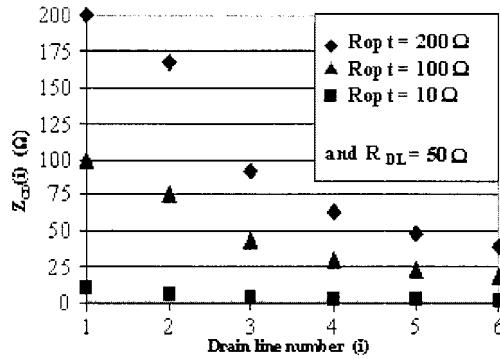

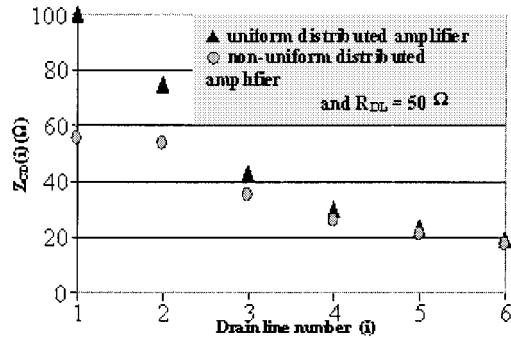

In the case of uniform distributed amplifiers integrating identical transistors, the optimum power load  $R_{\text{opt}}$  is constant for each drain-line section. Fig. 4 shows the optimum characteristic impedances  $Z_{\text{CD}(i)}$  of each drain-line section calculated from (2) for three different values of  $R_{\text{opt}}$  (10, 100, 200  $\Omega$ )

$$R_{\text{opt}} = 1/G_{\text{opt}} \quad \text{and} \quad Z_{\text{CD}(i)} = 1/G_{\text{CD}(i)}. \quad (7)$$

The equivalent optimum drain line (Fig. 3) shows that the design of a distributed power amplifier will be easier if the amplifier output is loaded by an impedance close to  $Z_{\text{CD}(n)}$  (usually inferior to 50  $\Omega$ ).

Fig. 4. Variation of the optimum characteristic impedances  $Z_{CD(i)}$  of each drain-line section for different optimum power loads  $R_{opt}$  (uniform distributed architecture).

Unfortunately, since most of the applications require a  $50\Omega$  output load, it is very advantageous for the designer to choose the transistor size leading to a characteristic impedance  $Z_{CD(n)}$  as close as possible to  $50\Omega$ . Therefore, looking at  $Z_{CD(6)}$  (see Fig. 4), it is clear that transistors having high  $R_{opt}$  (small size) are most interesting. In return, if the designer chooses a small size of transistor leading to a high  $R_{opt}$ , the first optimum drain-line section must synthesize a very high characteristic impedance  $Z_{CD(1)}$  (see Fig. 4). Finally, the difference between  $Z_{CD(1)}$  and  $Z_{CD(n)}$  is greatly increased so that the drain-line synthesis and matching are very difficult over wide bandwidths.

It is necessary to minimize the difference between  $Z_{CD(1)}$  and  $Z_{CD(n)}$  by using lower impedances  $R_{opt}$  (large size) for the first drain-line sections, while keeping high  $R_{opt}$  (small size) for the last sections. This conclusion has led us to implement nonuniform distributed architectures that enable to modify  $R_{opt}$  for each drain section by using different sizes of transistors.

### III. GENERALIZATION TO NONUNIFORM DISTRIBUTED POWER AMPLIFIERS

#### A. Topology of the Nonuniform Distributed Amplifier

This section explains how using a nonuniform distributed architecture makes it possible to minimize the difference between  $Z_{CD(1)}$  and  $Z_{CD(n)}$  so that power matching is easier. Indeed, the optimum power load  $R_{opt(i)}$  can be increased with  $i$  by decreasing the transistor width  $W(i)$  from  $i$  equals  $1 - n$ .

In the case of nonuniform distributed amplifiers, each transistor  $T(i)$  has a specific gatewidth  $W(i)$ . Therefore, the optimum power matching conditions ( $G_{IN}$ ,  $G_{OPT}$ ,  $P_{max}$ ), which were constant in the uniform case, now become ( $G_{IN(i)}$ ,  $G_{OPT(i)}$ ,  $P_{max(i)}$ ) and depend on the gatewidth  $W(i)$  of the transistor  $T(i)$ .

#### B. Design Methodology

The new design methodology of nonuniform distributed power amplifiers is based on the same principle as for the uniform distributed architecture. At first, the optimum power loads  $G_{IN(i)}$  and  $G_{OPT(i)}$  are determined for each gatewidth  $W(i)$  and the optimum characteristic conductances of gate- and drain-line sections are analytically expressed.

⇒ *Drain Line*: In the same manner as previously described for the uniform architecture, the characteristic conductances

$G_{CD(i)}$  can be successively determined. The first device  $T_{(1)}$  provides a reduced output power  $P_{OUT(1)}$  in comparison with its maximum output power capability  $P_{max(1)}$ , but ensures that the other transistors  $T_{(i \geq 2)}$  supply their maximum output power  $P_{max(i)}$ . The generalized optimum power matching structure is analytically determined to add the individual power contributions in the direction of the output port

$$G_{CD(1)} = G_{OPT(1)} \quad (8)$$

$$G_{CD(i \geq 2)} = \left( \frac{G_{OPT(1)}^2}{G_{DL} + G_{OPT(1)}} + \sum_{k=2}^i G_{OPT(k)} \right) \quad (9)$$

$$P_{OUT(1)} = \left( \frac{G_{OPT(1)}}{G_{DL} + G_{OPT(1)}} \right) \cdot P_{max(1)} \quad (10)$$

$$P_{OUT} = P_{OUT(1)} + \sum_{k=2}^n P_{max(k)} \quad (11)$$

where  $G_{CD(i)}$  is the optimum characteristic conductance of the  $i$ th drain-line section,  $P_{OUT(1)}$  is the output power of the first device  $T(1)$ ,  $P_{OUT}$  is the amplifier output power,  $T(k)$  is the  $k$ th transistor with a gatewidth  $W(k)$ ,  $G_{opt(k)}$  and  $P_{max(k)}$  are, respectively, the optimum output conductance and output power of the  $k$ th transistor  $T(k)$ , and  $G_{DL}$  is the dumping drain load. Its value is chosen equal to  $G_{CD(1)}$ .

It should be noted that, in the case of moderate bandwidth applications, the dumping load  $G_{DL}$  can be suppressed so that each transistor could be ideally power matched and yield its maximum output power. In this case, the optimum case becomes

$$G_{CD(i)} = \sum_{k=1}^i G_{OPT(k)} \text{ and } P_{OUT} = \sum_{k=1}^n P_{max(k)}. \quad (12)$$

Moreover, this new design methodology can be directly applied to nonuniform cascode distributed amplifiers since the conclusion of a constant ( $G_{opt}$ ,  $C_{opt}$ ) is true in the case of optimized cascode devices [7].

⇒ *Gate Line*: In the same manner as for the uniform case, gate-line sections are determined to match the input conductance  $G_{IN(i)}$  of each transistor  $T(i)$  so that equal gate voltage amplitudes could be obtained over the frequency band. To achieve the equal gate voltage condition, the characteristic conductances of gate-line sections are given by

$$G_{CG(i)} = \sum_{k=i}^n G_{IN(k)} \quad G_{GL} = G_{IN(n)}. \quad (13)$$

Moreover, the electrical lengths  $\theta_{CG(i)}$  and  $\theta_{CD(i)}$  of the corresponding gate- and drain-line sections must always verify

$$\theta_{CG(i)} = \theta_{CD(i)}. \quad (14)$$

As a conclusion, depending on the optimum power load  $G_{opt}$  (mS/mm) of the device process and on the amplifier output load ( $50\Omega$  or less), improved output power performances can be achieved by using nonuniform distributed architectures with tapered gate and drain lines following the constraints (8)–(13). This new design methodology of nonuniform distributed power amplifiers represents a unified method since it includes the

Fig. 5. Comparison of the optimum drain-line profiles between a uniform ( $T_{(1 \rightarrow 6)} = 300 \mu\text{m}$ ) and nonuniform amplifier ( $T_{(1)} = 600 \mu\text{m}$  and  $T_{(2 \rightarrow 6)} = 300 \mu\text{m}$ ).

particular case of uniform architectures and enable to make an efficient choice between the two amplifier topologies. Indeed, taking ( $G_{\text{IN}(k)}$ ,  $G_{\text{opt}(k)}$ ,  $P_{\text{max}(k)}$ ) constant and equal to ( $G_{\text{IN}}$ ,  $G_{\text{opt}}$ ,  $P_{\text{max}}$ ) in (8)–(11), and (13) enable to retrieve (2)–(5) of the uniform case.

### C. Comparison of Optimum Drain-Line Profiles for Uniform and Nonuniform Distributed Amplifiers

Section IV will report the design and measurement results of a nonuniform power distributed amplifier realized at the TriQuint Semiconductor Foundry, Richardson, TX, on its pseudodomorphic high electron-mobility transistor (pHEMT) process. For this particular design, we now explain and illustrate why a nonuniform distributed amplifier has been chosen instead of a uniform architecture. The selected architecture integrates a 600- $\mu\text{m}$  pHEMT as the first transistor  $T(1)$ , while the other transistors  $T(i \geq 2)$  are identical 300  $\mu\text{m}$  pHEMT.

Fig. 5 shows a comparison between the calculated optimum characteristic impedances  $Z_{\text{CD}(n)}$  of each drain-line section for two different topologies of the distributed amplifier as follows.

- A uniform distributed amplifier is calculated using (2) and (3) in the case of six identical 300- $\mu\text{m}$  transistors ( $R_{\text{opt}(300\mu\text{m})} = 100 \Omega$ ).

- A nonuniform distributed amplifier is calculated using (8) and (9) in the case of a 600- $\mu\text{m}$  device as first transistor ( $R_{\text{opt}(1)} = 56 \Omega$ ) followed by five identical 300- $\mu\text{m}$  devices ( $R_{\text{opt}(2 \leq i \leq 6)} = 100 \Omega$ ).

In the particular case of this pHEMT process, the nonuniform distributed amplifier has permitted to greatly minimize the difference between  $Z_{\text{CD}(1)}$  and  $Z_{\text{CD}(n)}$  ensuring an easier power matching design (see Fig. 5). Therefore, the nonuniform power distributed architecture has been selected since the uniform amplifier did not enable us to reach the specifications of 1-W output power up to 19 GHz.

## IV. APPLICATION TO A SINGLE-STAGE MMIC AMPLIFIER

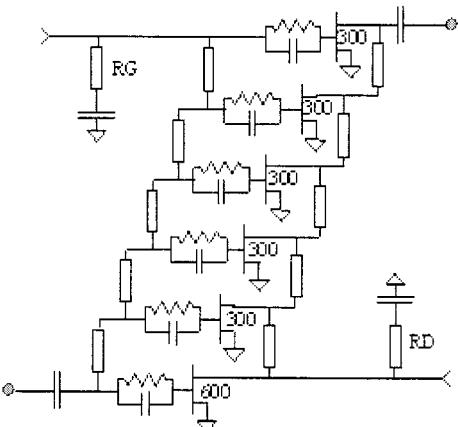

A nonuniform distributed power amplifier has been designed in cooperation with Thalès Laboratories, Massy, France, following this specific design procedure. The MMIC circuit has been manufactured using a 0.25- $\mu\text{m}$  power pHEMT process from the TriQuint Semiconductor Foundry. The single-stage amplifier integrates six amplifying cells (see Fig. 6). The first

Fig. 6. Schematic of the nonuniform MMIC amplifier.

transistor  $T(1)$  is a 600- $\mu\text{m}$  pHEMT, while the other transistors  $T(i \geq 2)$  are 300- $\mu\text{m}$  pHEMTs. For this nonuniform architecture (see Fig. 6), (8) and (9), giving the optimum characteristic admittances  $G_{\text{CD}(i)}$  of the drain-line sections, can be simplified using the following assumptions:

$$G_{\text{OPT}(1)} = G_{\text{OPT}(600\mu\text{m})} \approx 2 \cdot G_{\text{OPT}(300\mu\text{m})} \quad (15)$$

$$G_{\text{OPT}(i \geq 2)} = G_{\text{OPT}(300\mu\text{m})}. \quad (16)$$

### A. Nonlinear Modeling and Design Process

In a first step, the 300- and 600- $\mu\text{m}$  devices have been modeled using pulsed  $I$ – $V$  and pulsed  $S$ -parameter measurement. The optimum power loads provided by the foundry were then compared to nonlinear simulation results (a good agreement is obtained between the optimum power loads provided by the TriQuint Semiconductor Foundry and those obtained from simulation). Finally, the optimum power load of the 300- and 600- $\mu\text{m}$  devices have been found sensibly constant up to 20 GHz and are equal to [ $G_{\text{OPT}(300\mu\text{m})} = 10 \text{ mS}$ ,  $C_{\text{OPT}(300\mu\text{m})} = 0.18 \text{ pF}$ ,  $P_{\text{max}} = 24 \text{ dBm}$ ] and [ $G_{\text{OPT}(600\mu\text{m})} = 18 \text{ mS}$ ,  $C_{\text{OPT}(300\mu\text{m})} = 0.31 \text{ pF}$ ,  $P_{\text{max}} = 26.5 \text{ dBm}$ ], respectively.

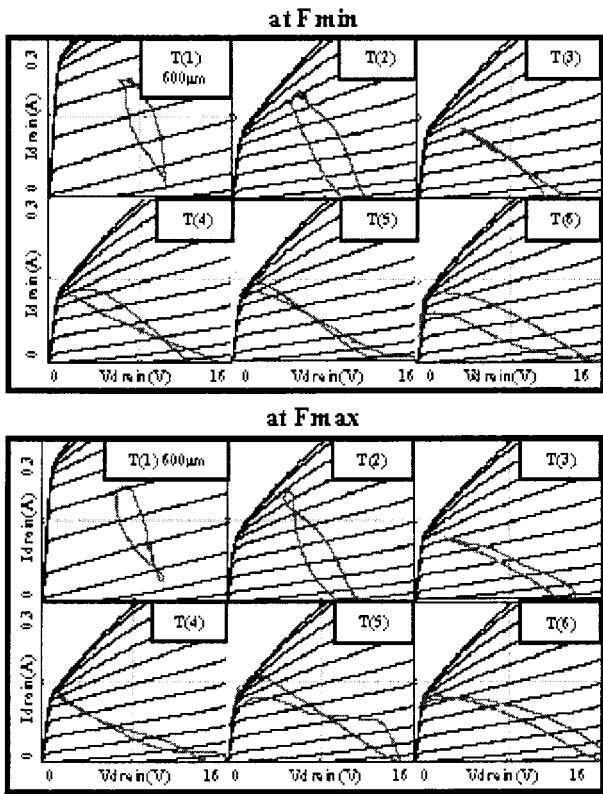

Uniform and nonuniform distributed amplifiers were initially designed and compared with the aim to supply 1-W output power and 20% power-added efficiency (PAE) over multi octave bandwidths. As previously explained (see Fig. 5), a nonuniform distributed architecture integrating a first device  $T(1)$  of double gatewidth offered the best tradeoff between output power, gain, and return losses. Therefore, given the preceding optimum power loads  $G_{\text{OPT}(600\mu\text{m})}$  and  $G_{\text{OPT}(300\mu\text{m})}$ , the tapered drain line has been optimized so that the first 600- $\mu\text{m}$  device supplies a reduced output power (10), but enables the five following 300- $\mu\text{m}$  devices to be almost ideally power matched. Fig. 7 shows the nonlinear simulation results for each device load line at  $f_{\text{min}}$  and  $f_{\text{max}}$ . In accordance with the preceding principle, it can be observed that the first device is affected by the dumping drain load  $G_{\text{DL}}$  and is not power matched, but enables the other devices to be almost ideally power matched.

The optimum tapered gate line has been obtained through a gate coupling capacitor profile along the input line. Discrete se-

Fig. 7. Simulated device load lines at  $f_{\min}$  and  $f_{\max}$  ( $T_{(1)} = 600 \mu\text{m}$  and  $T_{(2 \rightarrow 6)} = 300 \mu\text{m}$ ).

ries capacitors couple each active device to the input line and act as voltage dividers to ensure equal drive levels on the transistor gates [8]–[10]. Implanted GaAs resistors shunt the series metal–insulator–metal (MIM) capacitors to supply gate bias.

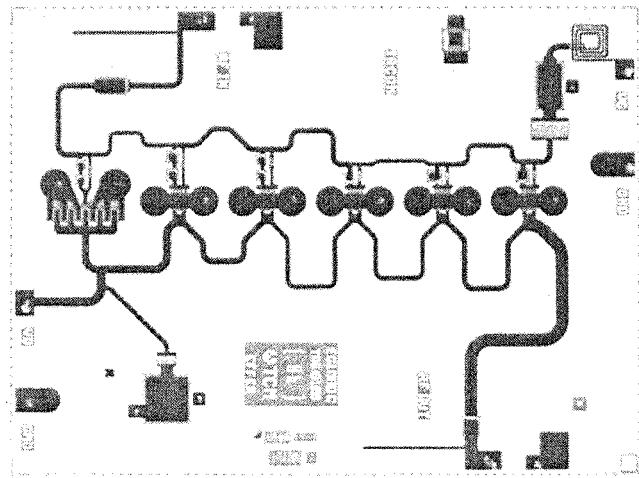

## B. Circuit Realization and Measured Performances

The nonuniform distributed power amplifier has been manufactured at the TriQuint MMIC Foundry, Richardson, TX, using a 100- $\mu\text{m}$ -thick GaAs substrate and 0.25- $\mu\text{m}$  power pHEMT. The main electrical parameters of this broad-band process are typically 295-mA/mm saturated current,  $-1$ -V pinchoff voltage and more than 16-V breakdown voltage for an associated power density of 800 mW/mm. The final circuit layout is shown in Fig. 8. It should be noted that the smallest values of gate coupling capacitances have been synthesized by two series capacitors in order to meet the minimum size constraint on MIM capacitors.

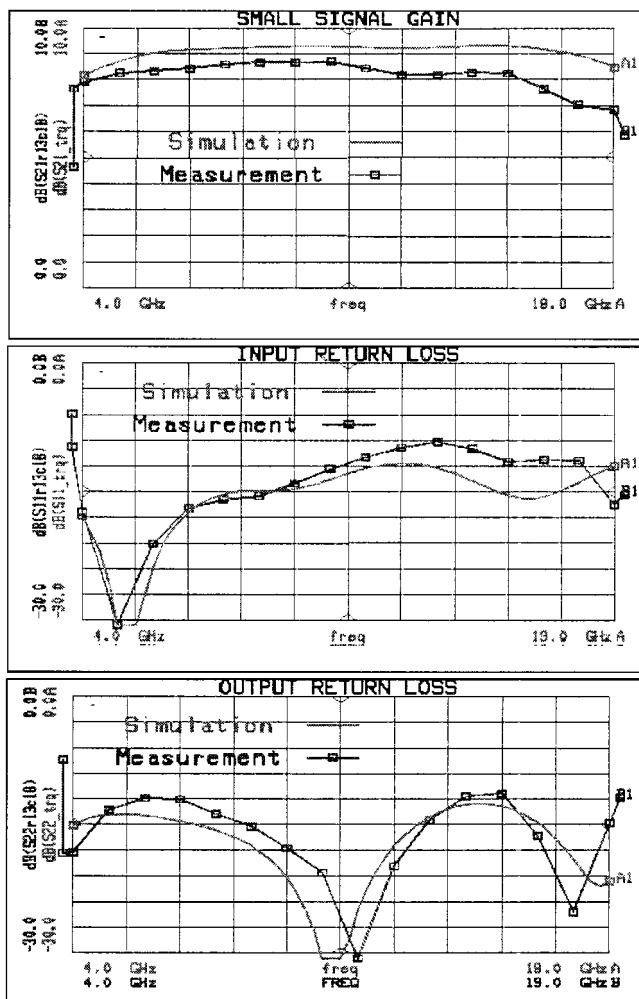

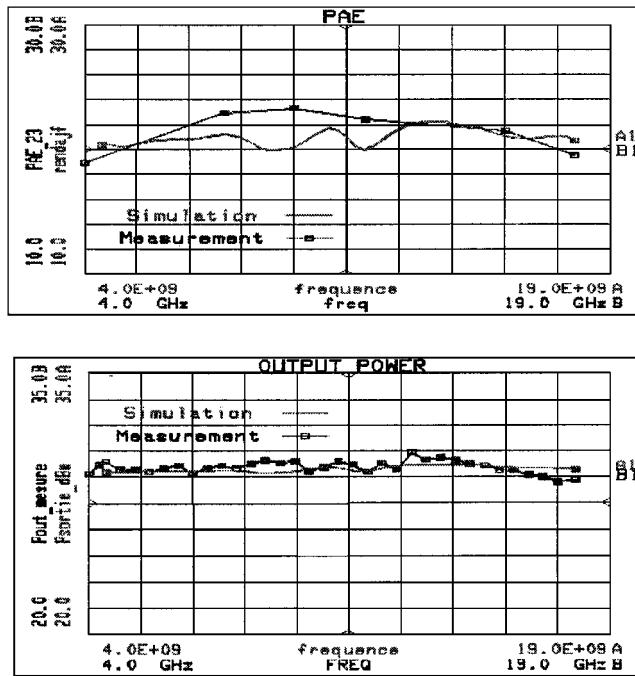

After wafer manufacturing, the nonuniform distributed amplifier was tested for dc operation and RF performances in class-A operation ( $V_{ds} = 8$  V,  $I_{ds} = 270$  mA). Fig. 9 shows a comparison between small-signal on-wafer measurements and simulations in the frequency band. A good agreement is obtained for input and output return losses that are lower than  $-10$  dB in all of the bandwidth. The measured linear gain is 1 dB less than the simulated one and lies around 8.5 dB. At an input power of 23 dBm, on-wafer continuous-wave (CW) power measurements exhibited 30-dBm output power.

The exact cause of the rolloff observed at 18 GHz for the on-wafer measured gain (Fig. 9) is not known at this time. It

Fig. 8. Nonuniform MMIC distributed power amplifier.

Fig. 9. Simulations and on-wafer measurements of small-signal gain and return losses.

seems that it is mainly due to the on-chip feature for the compensation of bonding wire effects at high frequency since bonding wires are not present under on-wafer conditions.

Fig. 10. Simulated and measured PAE and output power over the 4–19-GHz frequency band @ $P_{in} = 23$  dBm,  $V_{ds} = 8$  V and  $I_{ds} = 270$  mA.

TABLE I

COMPARISON WITH RECENTLY PUBLISHED BROAD-BAND POWER AMPLIFIERS

| Year | Stage | Trans. | Freq. (GHz) | Pout (dBm) | PAE (%) | Gain (dB) | Ref  |

|------|-------|--------|-------------|------------|---------|-----------|------|

| 2000 | 1     | PHEMT  | 2.8         | 35         | 20      | 9         | [11] |

| 2001 | 1     | PHEMT  | 2.18        | 25         | 27      | 27        | [12] |

| 2001 | 1     | HEMT   | 2.8         | 36         | 24      | 12        | [13] |

Test-fixture measurements have also been performed. The MMIC circuit was soldered on a molybdenum carrier and interfaced to the RF connectors with 13-mm-long  $50\text{-}\Omega$  microstrip alumina lines. The measured circuit exhibited 30-dBm CW output power and more than 20% PAE. Fig. 10 shows the good agreement obtained between predicted and measured output power and PAE up to 19 GHz.

All these results have been obtained after one foundry pass and without circuit tuning. For the sake of comparison, Table I presents performances obtained by three recently published broad-band power amplifiers.

## V. CONCLUSION

A new design methodology of nonuniform distributed power amplifiers has been reported in this paper. This method is a generalization of our previous work on uniform distributed amplifiers [5]. It is based on analytical expressions of the optimum input and output artificial lines making up the nonuniform distributed architecture. These relationships are based on the optimum power load of each device size. Furthermore, given the optimum power load as a function of gatewidth, a design criterion has been presented that enables an efficient choice be-

tween uniform and nonuniform distributed topologies. To validate this specific methodology, a nonuniform single-stage distributed power amplifier has been designed and manufactured at the TriQuint Semiconductor Foundry, Richardson, TX, using a  $0.25\text{-}\mu\text{m}$  pHEMT process. After one foundry pass, this MMIC amplifier demonstrated 1-W output power with 7-dB associated gain and a minimum of 20% PAE over a multi octave frequency band.

## REFERENCES

- [1] K. B. Niclas, W. T. Wilser, T. R. Kritzer, and R. R. Pereira, "On theory and performance of solid-state microwave distributed amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 447–456, June 1983.

- [2] J. B. Beyer, S. N. Prasad, and G. K. Hohenwarter, "MESFET distributed amplifier design guide-lines," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 268–275, Mar. 1984.

- [3] K. B. Niclas, R. R. Pereira, and A. P. Chang, "On power distribution in additive amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 1692–1700, Nov. 1990.

- [4] M. Campovecchio, B. Le Bras, M. Lajugie, and J. Obregon, "Optimum design of distributed power FET amplifiers: Application to 2–18 GHz MMIC module exhibiting improved power performances," in *IEEE MTT-S Int. Microwave Symp. Dig.*, San Diego, CA, 1994, pp. 125–128.

- [5] M. Campovecchio, B. Le Bras, R. Hilal, M. Lajugie, and J. Obregon, "Large signal design method of distributed power amplifiers applied to a 2 to 18 GHz GaAs chip exhibiting high power density performances," *Int. J. Microwave Millimeter-Wave Computer-Aided Eng.*, vol. 6, no. 4, pp. 259–269, 1996.

- [6] F. Blache, J. M. Nebus, P. Bouysse, and J. P. Villotte, "A novel computerized multiharmonic active load-pull system for the optimization of high efficiency operating classes in power transistors," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1995, pp. 1037–1040.

- [7] J. P. Fraysse, J. P. Viaud, M. Campovecchio, P. Auxemery, and R. Quere, "A 2-W high-efficiency 2–8-GHz cascode HBT MMIC power distributed amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, Boston, MA, June 2000, pp. 529–532.

- [8] Y. Ayasli, S. W. Miller, R. Mozz, and L. K. Hanes, "Capacitively coupled travelling wave power amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1704–1709, Dec. 1984.

- [9] Y. Ayasli, "Decade bandwidth amplification at microwave frequencies," *Microwave J.*, vol. 17, no. 4, pp. 70–78, Apr. 1974.

- [10] P. Dueme, G. Aper, and S. Lazar, "Advanced design for wideband MMIC power amplifiers," in *GaAs IC Tech. Symp. Dig.*, 1990, pp. 121–124.

- [11] S. Lee, B. Green, K. Chu, K. J. Webb, and L. F. Eastman, "Demonstration of a high efficiency nonuniform monolithic gallium-nitride distributed amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, Boston, MA, 2000, pp. 549–552.

- [12] A. S. Virdee and B. S. Virdee, "A novel high efficiency multi octave amplifier using cascaded reactively terminated single-stage distributed amplifiers for EW system applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Phoenix, AZ, 2001, pp. 519–522.

- [13] B. M. Green, V. Tilak, S. Lee, F. Kim, J. A. Smart, K. J. Webb, J. R. Shealy, and L. F. Eastman, "High-power broadband AlGaN/GaN Hemt MMIC's on SiC substrates," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Phoenix, AZ, 2001, pp. 1059–1062.

**Cedric Duperrier** was born in Limoges, France, on June 25, 1974. He received the Post-Graduate Diploma in microwave communications from the University of Limoges, Limoges, France, in 1998, and is currently working toward the Doctor degree in electronic engineering at the University of Limoges.

Since 1998, he has been with the Institut de Recherche en Communications Optiques et Microondes (IRCOM) Laboratory, University of Limoges, where he is currently involved with distributed power amplifiers and microwave nonlinear circuit design.

**Michel Campovecchio** was born in Angers, France, in 1964. He received the Ph.D. degree in electronics from the University of Limoges, Limoges, France, in 1993.

In 1989, he was with the Thomson MMIC Foundry, Paris, France, where he was involved with FET nonlinear modeling. Since 1989, he has been with the Institut de Recherche en Communications Optiques et Microondes (IRCOM) Laboratory, University of Limoges, where he became an Associate Professor in 1994. His research interests include nonlinear circuit design and modeling, wide-band power amplifiers and high-speed amplifiers for 40 Gb/s optical communication (OC).

**Laurent Roussel** was born in Armentières, France, in 1965. He received the Electronic Engineering Degree from the University of Lille Flandres & Artois, Lille, France, in 1988.

He then joined Thomson-CSF, Paris, France, where he was involved in solid-state power-amplifier module design. He is currently with THALES Microwave, Massay, France, where he is involved in MMIC design for phased-array module.

**Monique Lajugie**, photograph and biography not available at time of publication.

**Raymond Quéré** (M'88-SM'99) received the Engineer and French Agregation degrees in applied physics from the Ecole National Supérieure d'Electrotechnique, Electronique, Informatique et Télécommunications (ENSEEIHT) Toulouse, Toulouse, France, in 1976 and 1978, respectively, and the Ph.D. degree from the University of Limoges, Limoges, France, in 1989.

In 1989, he became a Professor at the Technology Institute of Electrical Engineering (IUT), Brive, France, where he is involved in research concerned with nonlinear design and modeling of microwave circuits, with a special emphasis on nonlinear stability analysis of potentially unstable circuits such as oscillators, frequency dividers, and power amplifiers. He is also strongly involved with nonlinear characterization and modeling of microwave active devices based on pulsed measurements techniques.

Dr. Quéré is a member of the Technical Committee of the European Microwave Conference. He was a reviewer for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.